IBISモデルの歴史と分類

IBISモデルは1993年にVersion 1.1がリリースされ、30年弱の歴史があります。ここではその歴史を紐解きながら、3種のIBISモデルである「伝統的なIBISモデル」、「IBIS-AMIモデル」、「Power Aware IBISモデル」について説明します。

IBISモデルの歴史

1993年にIBIS Open Forumが設立され、Version 1.1がリリースされました。

- 1991年 PCIバスの規格を制定するためPCI-SIG設立

- 1993年 初代Pentium登場

PCの普及が始まった時代です。

IBISモデルの立ち位置

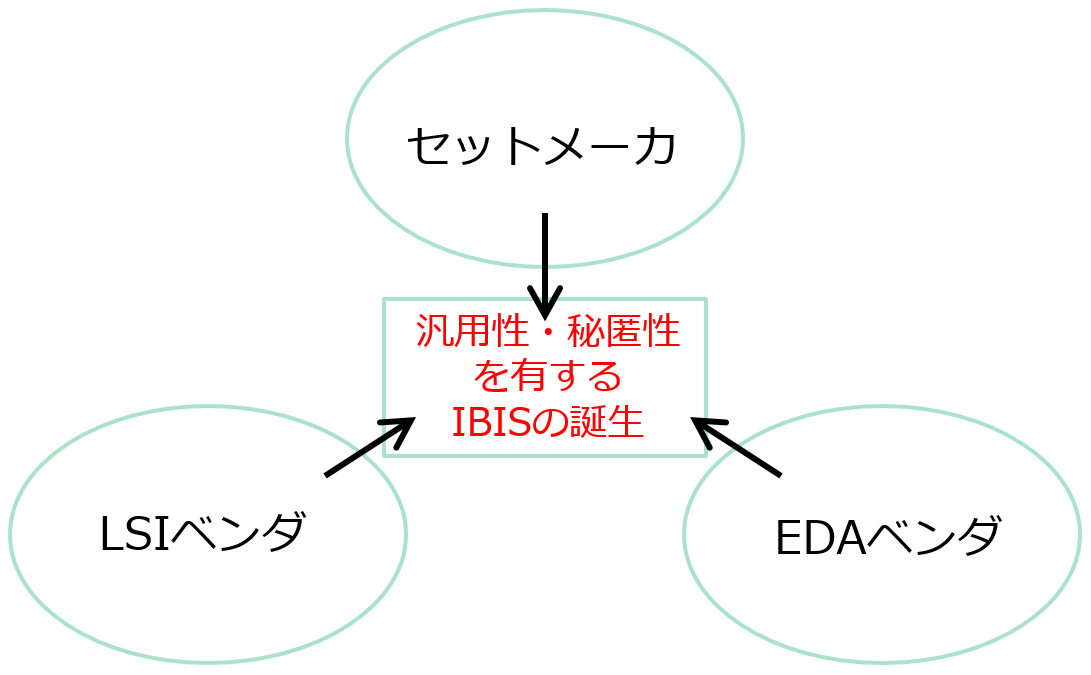

IBISは「LSIベンダ(IBISモデルの作成者)」、「セットメーカ(IBISモデルの使用者)」、「EDAベンダ」の3者の関係がWin-Winとなる様に策定されました。

IBISモデルの改版履歴

以下にIBISモデルの改定履歴を示します。現在は目的に応じて、「伝統的なIBISモデル」、「IBIS-AMIモデル」、「Power Aware IBISモデル」の3種が存在する形となっています。

| IBIS 1.0 | ||

| IBIS 1.1 | 1993.06 | |

| IBIS 2.0 | 1994.06 | |

| IBIS 2.1 | 1995.12 | ECL、PECL、差動サポート、Pin Mapping、V-T波形テーブル等の機能拡張。 |

| IBIS 3.0 | 1997.06 | |

| IBIS 3.1 | 1998.07 | |

| IBIS 3.2 | 1999.01 | モデルセレクタ、パッケージモデル、EBD記述、Series素子等の機能拡張。 Driver Schedule機能搭載。 基本的なシミュレーションはほぼ実行可能に。 |

| IBIS 4.0 | 2002.07 | |

| IBIS 4.1 | 2004.02 | |

| IBIS 4.2 | 2006.06 | Waveformデータ拡張、レシーバ閾値等の機能拡張。 伝統的なIBISモデルの完成。 マルチリンガルモデル拡張(SPICE、Verilog-A、Verilog-AMS、VHDL-AMS等)。 |

| IBIS 5.0 | 2008.08 | 高速シリアル伝送解析に用いられるIBIS-AMIモデルの誕生。 Power aware IBIS、EMI Parameter等の機能拡張。 |

| IBIS 5.1 | 2012.08 | IBIS-AMIの更新等。 |

| IBIS 6.0 | 2013.09 | IBIS-AMIの更新等。 |

| IBIS 6.1 | 2015.09 | IBIS-AMIの更新(PAM4)等。 電源ピン、パッケージモデル等の機能拡張。 |

| IBIS 7.0 | 2019.03 | インターコネクトモデルのサポート、 IBIS-AMIバックチャネル(Tx-Rx間のリンクトレーニング)のサポート等。 |

| IBIS 7.1 | 2021.12 | IBIS-AMIのDDR(DCオフセット)対応、 基板モデルの高周波対応(EMD記述)、 ダイ・電源容量モデルの高度化。 |

| IBIS 7.2 | 2023.01 | リドライバシミュレーション改善, PMAn(PAM4以外)対応 [Ex.USB4ver2-PAM3], DDR5向けクロックタイム対応, EMDモデル改善 |

- IBISモデルは新しいバージョンがリリースされても下位互換は維持出来る様になっています。また、IBISモデル内のバージョン表記([IBIS Ver])が6.1でも中身は4.2のモデルで構成されている場合があります。

伝統的なIBISモデル

初期の伝統的なIBISモデル

初期のIBISモデルはシングルエンド回路を如何に効率良く解析するかを考えて作られました。

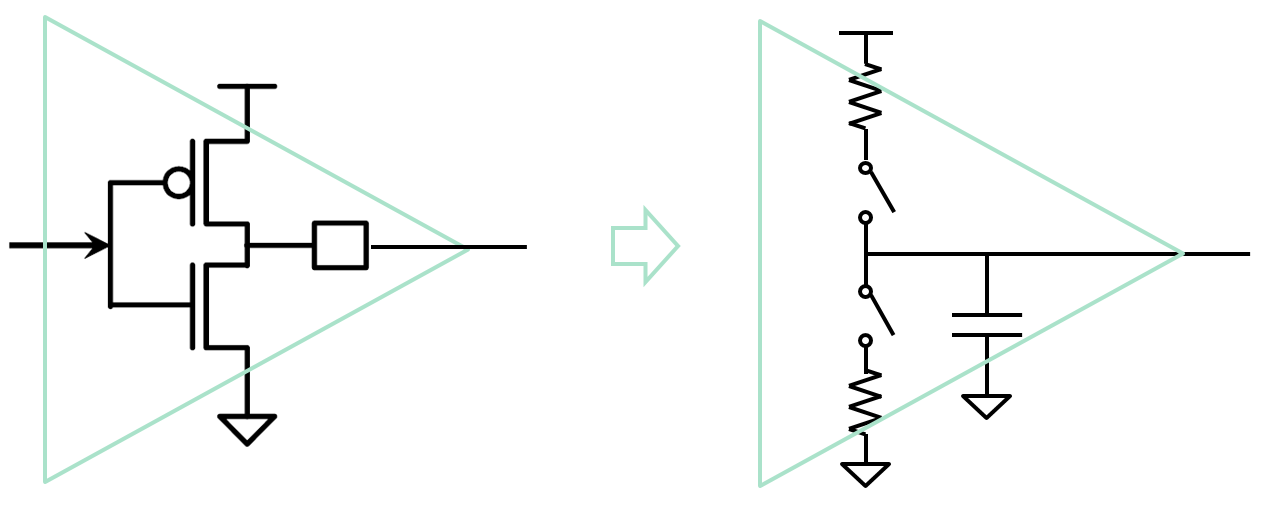

伝統的なIBISモデルの構造

伝統的なIBISモデルはデバイスの特性を極力シンプルに

- ドレイン – ソース間のon抵抗

- 立ち上がり/立ち下がり時間

- 容量(寄生容量)

の3特性によりモデル化を行っています。

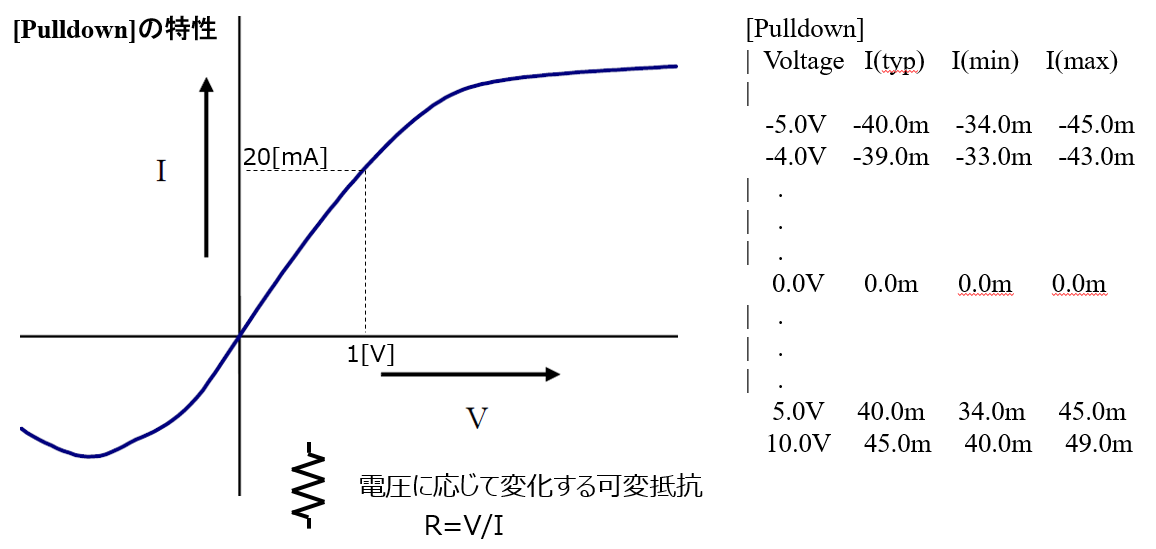

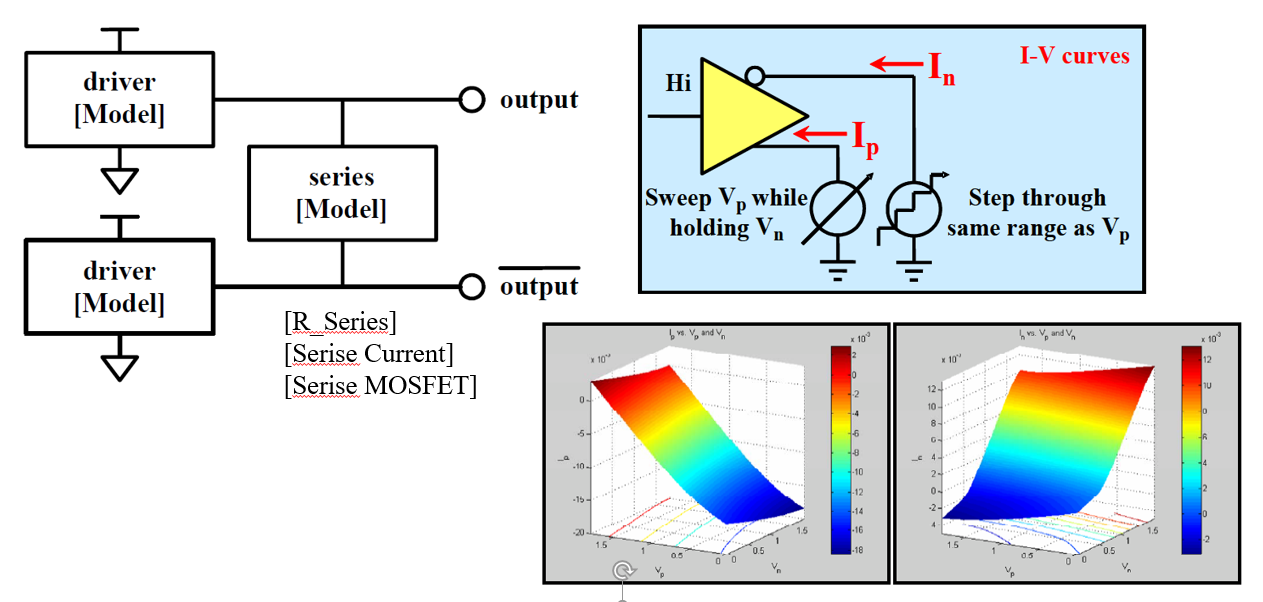

on抵抗特性の表現

IBISモデルではon抵抗特性を、実際のICの特性に従い、電圧Vと電流Iの関係をTABLE形式(プロット曲線)で表現します。

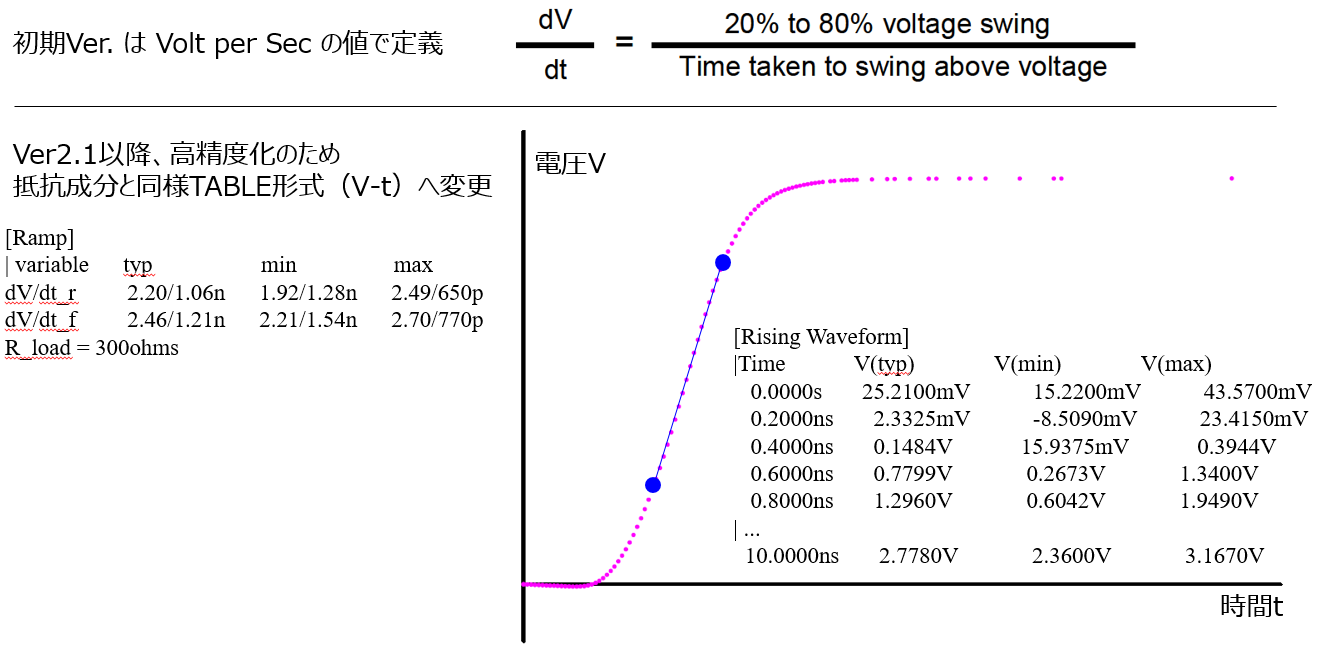

立ち上がり/立ち下がり時間の表現

初期のIBISモデルは立ち上がり/立ち下がり時間をVolt per Sec (Ramp)の値で定義していました。しかし、次第に高速化する信号に対しデバイスの特性を十分に表せているとは言えない状況でした。そこで、より正確に波形を表現するための手段として、TABLE形式であるWaveform記述がVersion 2.1から採用されました。

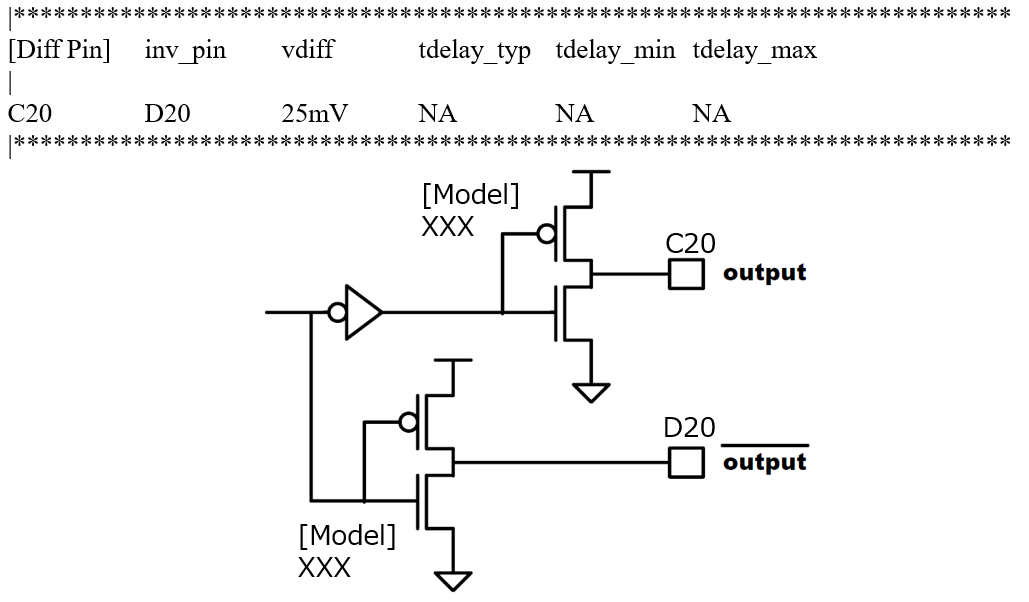

差動信号への対応

信号の高速化によって、差動信号への対応ニーズも高まりました。差動信号のモデルは[Diff Pin]記述を用いて、単線用のIBISモデルをそのまま疑似的に用いて対応しました(Version 2.1)。

series [Model]

差動端子では端子間の相関特性も存在します。単線用のIBISモデルをそのまま差動信号にする形では相関特性を表現できない為、series [Model]による特性の記述が検討されました。その中で様々な形式のモデルが発表されましたが、現在は単線用の記述をそのまま差動化したシンプルな形式のモデルが多く普及する形となっています。

プリ/ディエンファシスによる波形整形

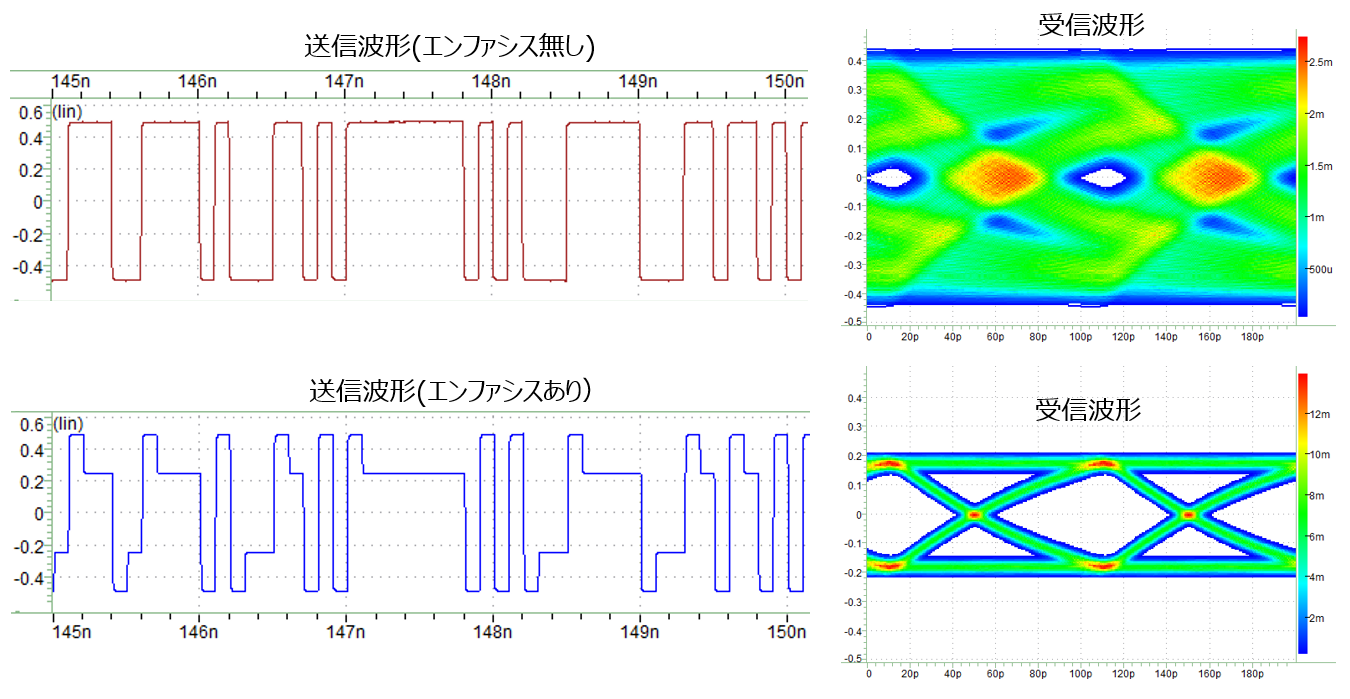

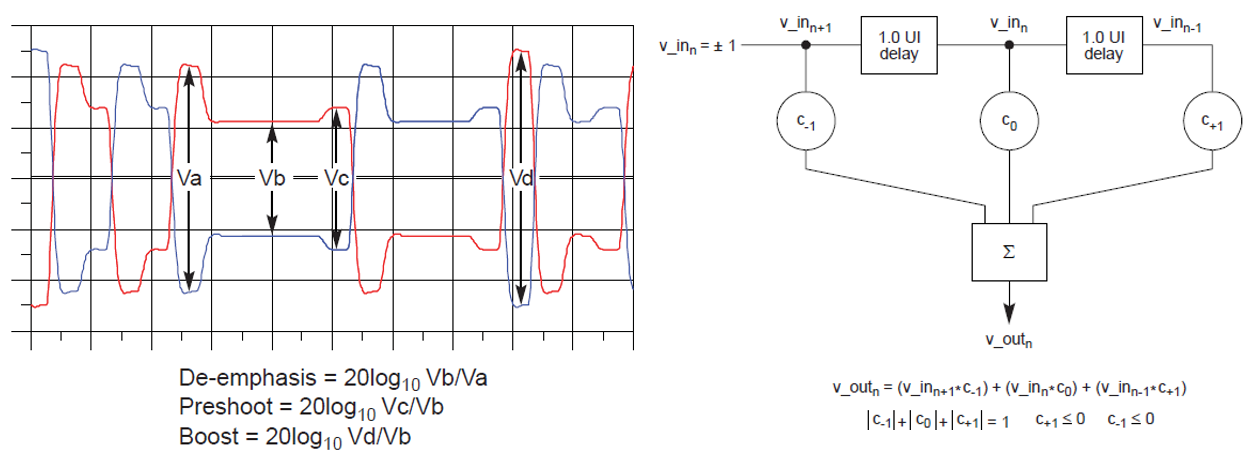

差動信号がさらに早くなると、出力波形のプリ/ディエンファシスによる波形整形が行われるようになりました。

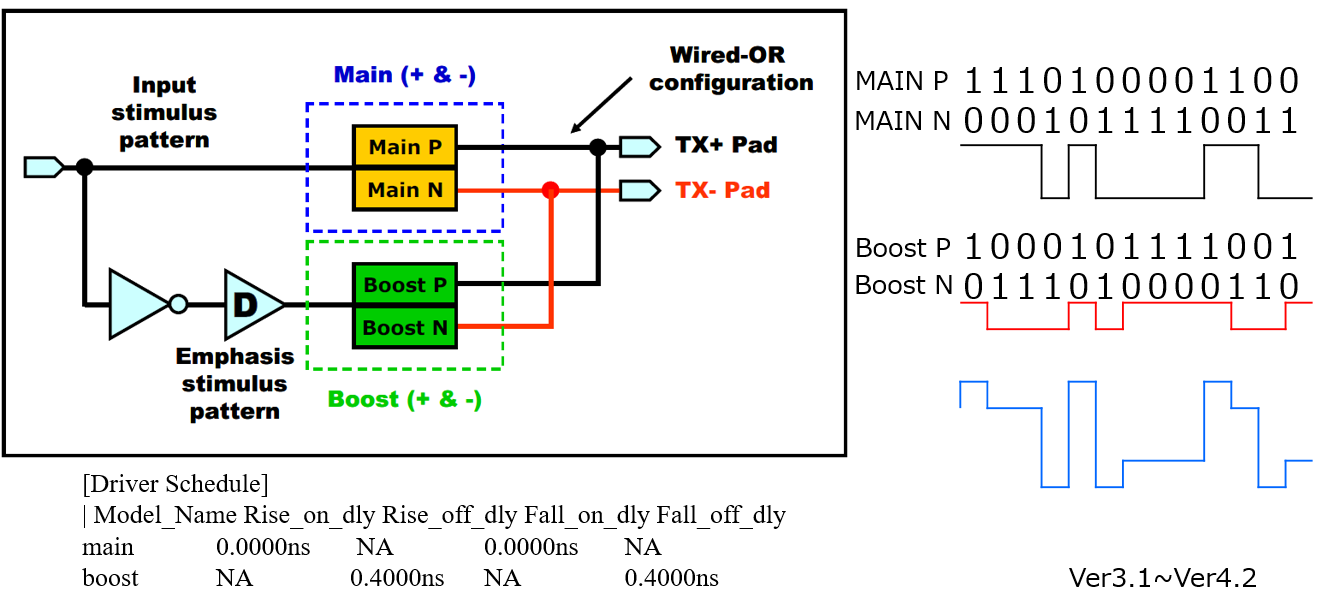

伝統的なIBISモデルによる波形エンファシスの表現

エンファシス機能を実現する為にDriver Schedule機能が誕生しました。複数のバッファをずらして動作させる事で、エンファシス波形を表現しています。

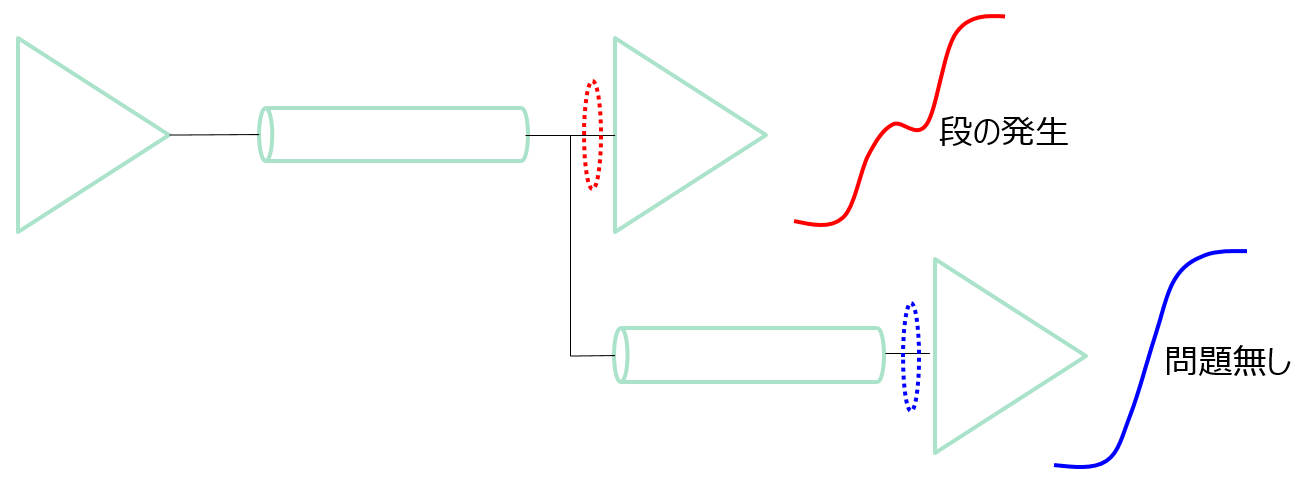

Over-Clocking問題

伝統的なIBISモデルはこの様に適宜モデル構成をアップデートし、信号の高速化に対応してきました。しかし、2Gbps程度の信号速度からRiseとFallの2つのWaveform波形のタイミングがオーバーラップしてしまうOver-Vlocking問題に行き当たり、信号の精度が出難い状況となってしまいました。

この問題に対応する為に、次世代のIBISモデル規格についての議論がなされ、IBIS-AMIモデルに落ち着くまでVerilog-AやVerilog-AMS、SPICEの組み込み等様々な手法が提案されてきました(Version 4.1、Version 4.2)。

IBIS-AMIモデル

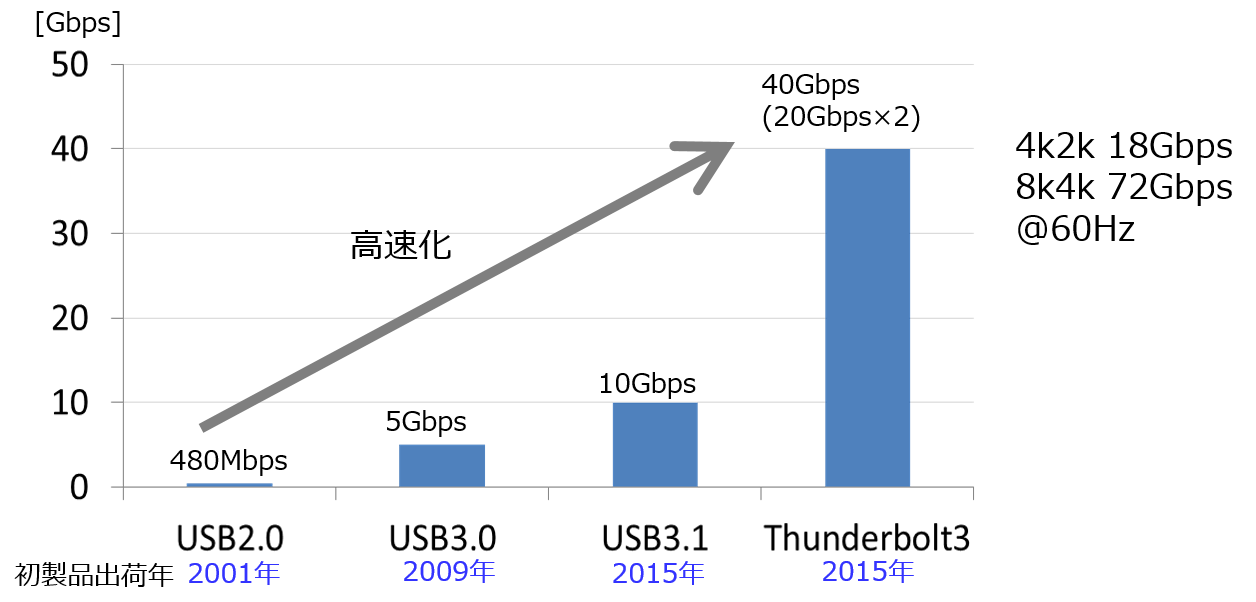

ますます高速化する信号規格

信号は高速化を続けており、それに対応して波形の制御は年々複雑化になっています。

IBIS-AMIモデルの特徴

IBIS-AMIモデルは伝統的なIBISモデルからの拡張をやめ、新規に作成されました。畳込み積分の概念を持ち込み、高速信号に流れる莫大な量のbit演算を高速に処理できます。

プログラミングによる記載により、ICの動作記述が容易になり秘匿性を向上させています。高速化が進むとICの設定一つで波形が大きく変わる為、ICベンダ側としては補正方法は秘匿にしておきたいという思いが生じます。

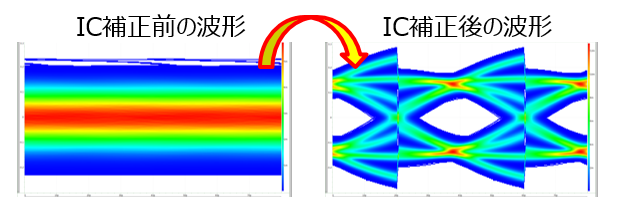

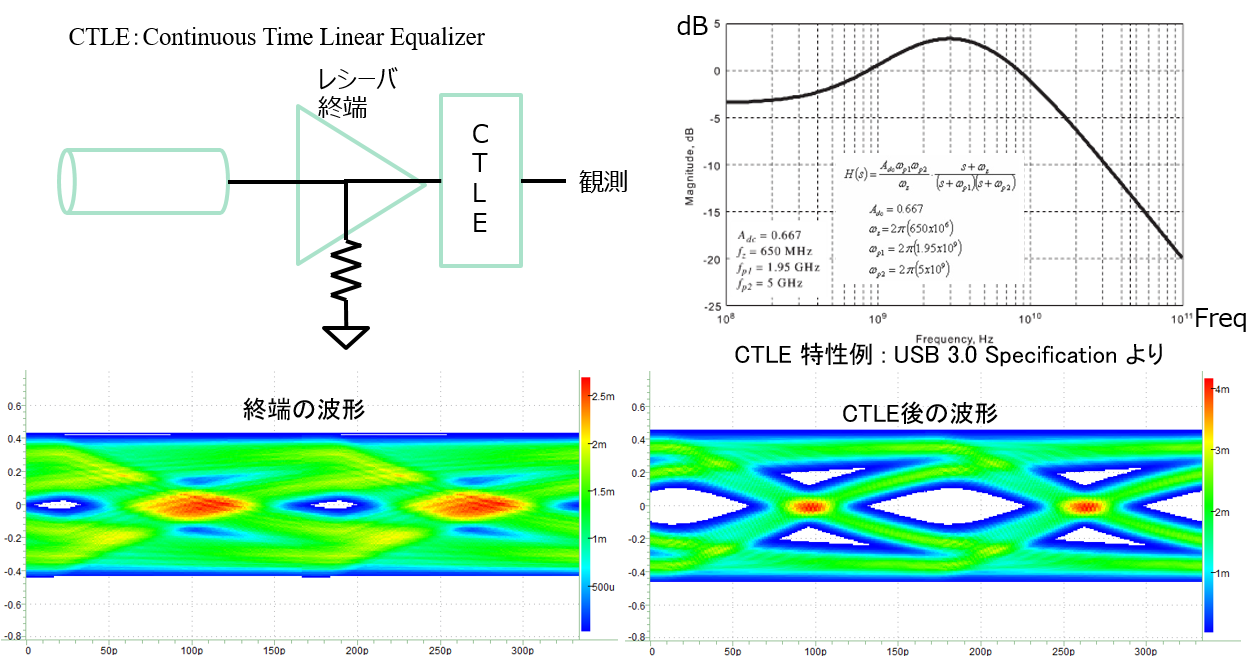

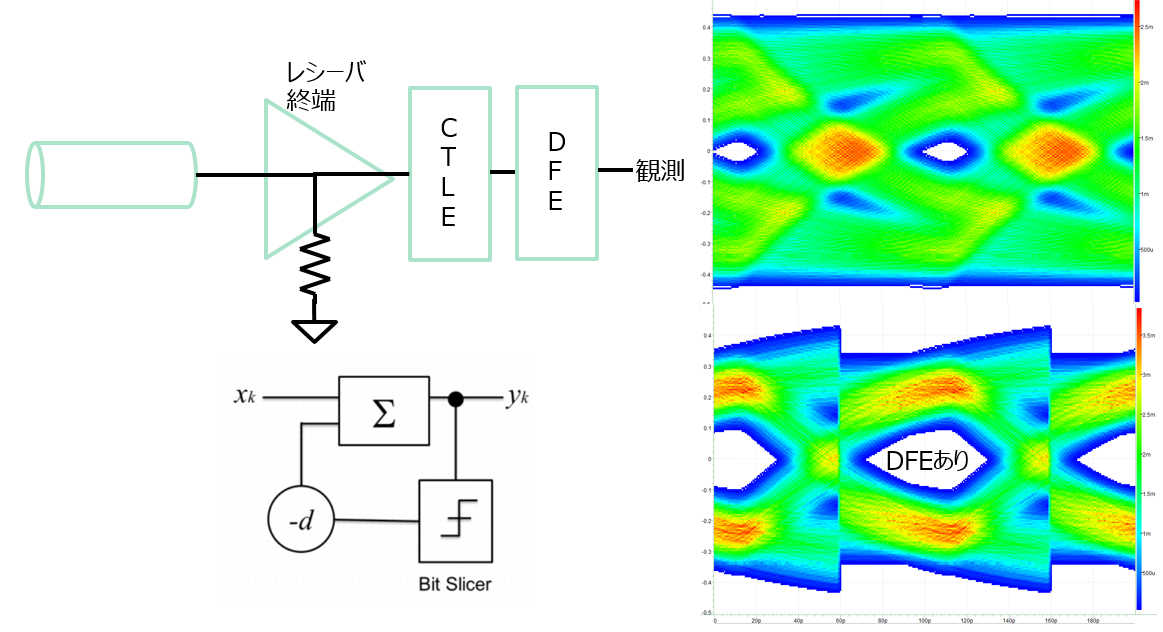

CTLEによる波形補正

高速化される(2Gbps超)と、受信側にCTLE(Continuous Time Linear Equalizer)回路が搭載され、波形をアナログ補正し波形を整形するようになりました。CTLEの特性はS-parameterのように周波数とdBの関係で表すことが出来ます。IBIS-AMIモデルにはこれら補正の特性も含まれた上でモデルの提供が行われます。

プリシュートによる波形補正

一例としてPCI Express Gen3 (8Gbps/lane)では、波形の出力側ICにプリ/ディエンファシスの発展版であるプリシュートが搭載されました。

DFEによる波形補正

更に高速化すると受信側ICにCTLE回路だけでなく1bit単位を主とし、デジタル的にフィードバックを行い波形を補正するDFE(Decision feedback Equalizer)が搭載される様になりました。

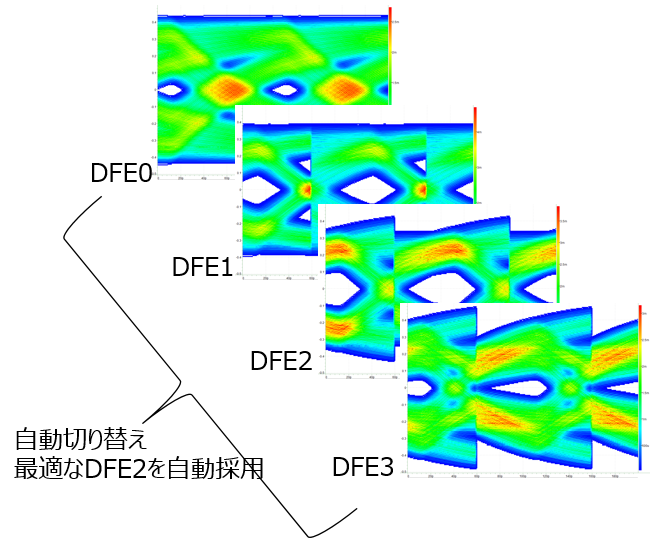

アダプティブイコライザ

近年の高速伝送用ICは自分自身で最適なイコライザ値を判断するようになっています(アダプティブイコライザ)。以前は実測時のICのレジスタ設定と同様になる様、シミュレーション設定を手作業で変える必要がありましたが、IBIS-AMIモデルはアダプティブイコライザを模擬できる様になっているため自動でシミュレーションを行う事が可能です。シミュレーションエンジニアはこれらプリエンファシス、プリシュート、CTLE、DFE、アダプティブイコライザがある事を理解した上でシミュレーションの設定が適切になっているか確認を行う必要があります。

Power Aware IBISモデル

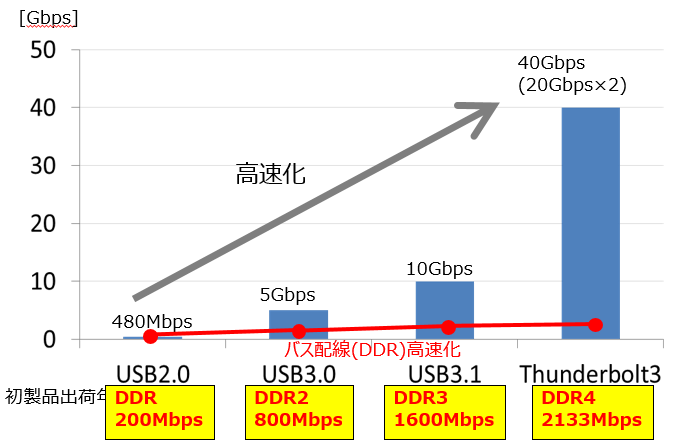

バス配線の高速化

バス配線が行われるであるDDRメモリもUSB等の差動シリアル伝送と同様に高速化が進んでいます。差動シリアル伝送に比べ遅い伝送速度の様に思えますが、配線の本数が並列に64本等と複数存在する為、バス配線としての転送速度は非常に速いものになります。

バス配線で発生する問題

バス配線においては、複数の信号駆動源が同時に動作する形になります。その場合、共通に接続された電源配線に大きなノイズ、同時スイッチングノイズが発生します。電源が変動すると結果的に信号波形も変動する為、バス配線時、電源の変動も加味して波形を表現可能なPower Aware IBISモデルが必要となってきました。

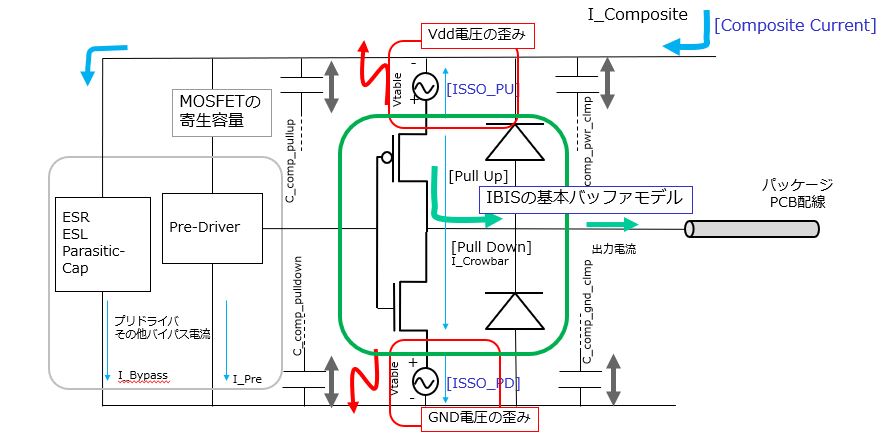

Power Aware IBISモデルの構成

Power Aware IBISモデルは伝統的なIBISモデルに対し[Composite Current]、[ISSO PU]、[ISSO PD]といったキーワードを足して表現を行います。それぞれTABLE形式にてI-t、V-I、V-I特性を表し、電源ノイズ・回路の特性を表現してゆく事になります。