IBIS Specificationで規定されている多数のキーワードの中で、主要なキーワードについて、その概略を説明します。

File Header Information セクション

- IBISファイルに関する情報やデータに関する基本的な情報が記載されています。ここには以下のキーワードが含まれます。

| キーワード | 必須 | 記述 |

| [IBIS Ver] | はい | IBISモデルのバージョン |

| [Comment char] | いいえ | コメントの識別子を変更します。デフォルトはパイプ(|)に設定 |

| [File Name] | はい | ファイル名。全てのファイル名は小文字を使います。IBISファイルの拡張子は (.ibs) |

| [File Rev] | はい | ファイルの改訂レベル。仕様は改訂にレベルを割り当てるためのガイドラインを含みます。 |

| [Date] | いいえ | ファイル作成日 |

| [Source] | いいえ | IBISモデルの元となったデータ(データシート、実測、シミュレーションなど)を記載 |

| [Notes] | いいえ | コンポーネントまたはファイルに特有のメモ。このモデルを使う上での重要な注意事項や制限事項が書かれている場合があります。 |

| [Disclaimer] | いいえ | 免責など法的な必要事項 |

| [Copyright] | いいえ | IBISファイルの著作権 |

Table 2.1 – Headerセクションのキーワード

Component Description セクション

- コンポーネントのpinoutやpin to bufferマッピングやパッケージとピンの電気的特性などデバイスの『データシート』に記載されている情報が含まれます。

| キーワード | 必須 | 記述 |

| [Component] | はい | モデル化されているコンポーネント名。多くの場合、業界標準の部品名称が使われます。1つのIBISファイルに、複数の[Component] が含まれることがあります。 |

| [Manufacturer] | はい | コンポーネントの製作者名 |

| [Package] | はい | ピンのデフォルトのパッケージパラメータが、抵抗(R_pkg)、インダクタンス(L_pkg)、キャパシタンス(C_pkg)で定義されます。Typ値だけでなく、範囲(Min、Max)が定義できます。 |

| [Pin] | はい | ピンとバッファモデルの割り当て情報が定義されています。モデルの作成者、このキーワードで個別のピン毎の R, L, C データのリストを作成することもできます。 |

| [Package Model] | いいえ | コンポーネントのモデルが、外部パッケージのモデルを含む場合(もしくは IBIS ファイルの範囲中でキーワード [Define Package Model] を使う場合)、そのパッケージモデルの名前を示します。 |

| [Pin Mapping] | いいえ | バッファの電源、グラウンドの接続情報を持たせたいときに、このキーワードが使われます。この情報は、複数出力のスイッチングのシミュレーションを行う時に必要になることがあります |

| [Diff Pin] | いいえ | 差動ペアのような相補的に動作するバッファの関連付けに使用されます |

| [Model Selector] | いいえ | コンポーネントで物理的に同じピンに対して、いくつかのバッファを定義しておき、シミュレーション毎に選択できるようにするために、このキーワードが使用されます。 通常は、IBIS の各々のピンは1つのバッファのみを参照します |

Table 2.2 – Componentセクションのキーワード

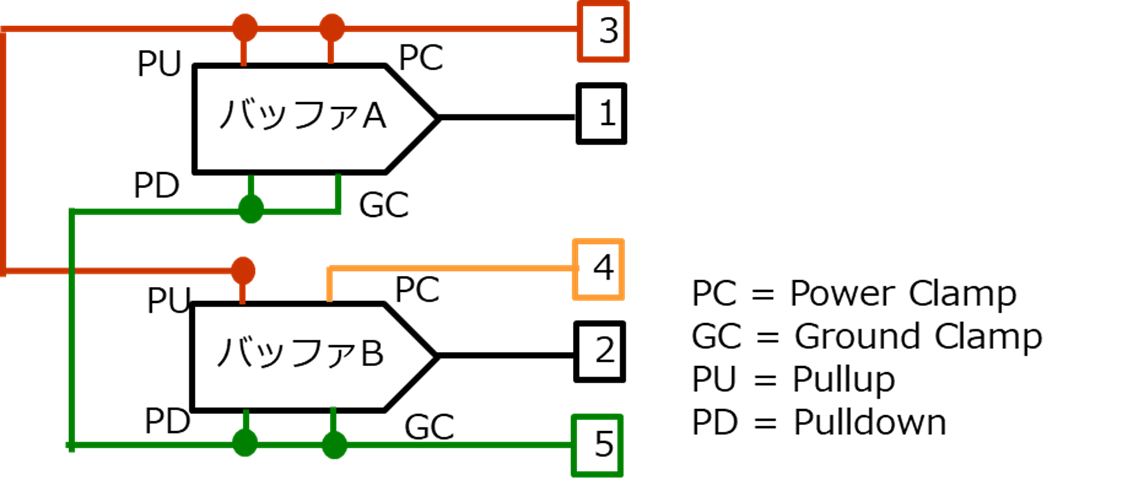

Pin Mapping

| キーワード: | [Pin Mapping] |

| 必須: | いいえ |

| Sub-Params: | pulldown_ref, pullup_ref, gnd_clamp_ref, power_clamp_ref, ext_ref |

| 概要: | 個々のバッファと電源、GNDピンの接続情報を定義します。 |

- 以下の例では、バッファA(1ピン)が3.3V電源(3ピン)とGND(5ピン)に接続し、バッファB(2ピン)が3.3V電源(3ピン)と5.0V電源(4ピン)とGND(5ピン)に接続する情報が定義されています。

|*****************************************************************

[Pin Mapping] pulldown_ref pullup_ref gnd_clamp_ref power_clamp_ref ext_ref

1 VSS VCC3 VSS VCC3

2 VSS VCC3 VSS VCC5

3 NC VCC3 | 3.3 V supply pin

4 NC VCC5 | 5.0 V supply pin

5 VSS NC | Ground pin

|*****************************************************************

図-2.1 Pin Mappingの定義例

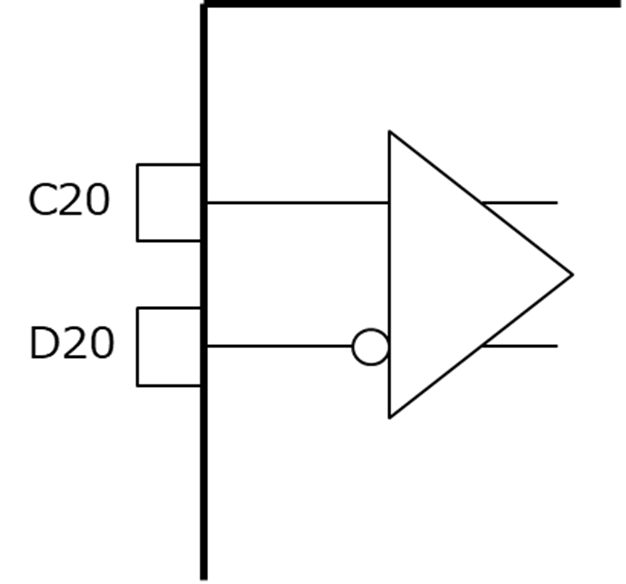

Diff Pin

| キーワード: | [Diff Pin] |

| 必須: | いいえ |

| Sub-Params: | inv_pin, vdiff, tdelay_typ, tdelay_min, tdelay_max |

| 概要: | 2つのピンの差動ペアを定義します。 |

| 注意事項: | [Diff Pin]はピンリストの後に記載されており、5つのパラメータを持ちます。ピンの名前は必須で、[PIN]セクションの名前と一致しなければなりません。他のすべてのパラメータは値として「NA」を使用することが出来ます。ただし、「NA」は0と等価ではないことに注意してください。[Diff Pin] 自体が定義されていないことがあるため、定義されているか確認する必要があります。 |

- 以下の例では、C20ピンとD20ピンが差動ペアとして定義されています。

|*****************************************************************

[Diff Pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

|

C20 D20 25mV NA NA NA

|*****************************************************************

図-2.2 Diff Pinの定義例

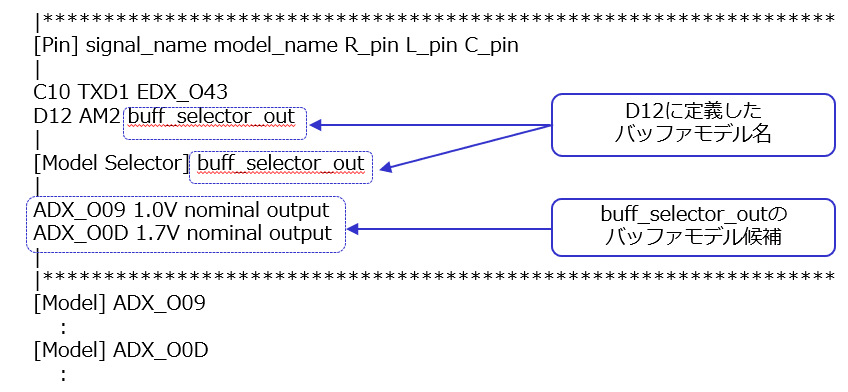

Model Selector

| キーワード: | [Model Selector] |

| 必須: | いいえ |

| 概要: | コンポーネントのバッファの駆動能力、ODT(On-Die-Termination)、電源電圧の切り替えに使用します。 |

| 注意事項: | シミュレータによって、Model Selectorのキーワードが対応していないものもあるため、Model Selectorがどの様に選択されているのかを把握し、正しいModel Selectorを選択する必要があります。 |

- 以下の例では、D12ピンにModel Selectorを使用した“buff_selector_out”が定義されています。ユーザは“buff_selector_out”の中から使用するバッファモデル(ADX_O09またはADX_O0D)を選択できます。

C10ピンはModel Selectorを使用していない例です。

Model Statement セクション

- 個々のバッファの入力時の閾値や、I-V特性、出力電圧対時間特性などが定義されています。

- 以下のキーワードを含みます。

※ISSO PD, ISSO PU, Composite Currentについては、「Power Aware IBIS Model」で説明します。

Model

| キーワード: | [Model] |

| 必須: | はい |

| Sub-Params: | Model_type, Polarity, Enable, Vinl, Vinh, C_comp, C_comp_pullup, C_comp_pulldown, C_comp_power_clamp, C_comp_gnd_clamp, Vmeas, Cref, Rref, Vref |

| 概要: | モデルとその属性を定義します。 |

| [Model] パラメータ | 必須 | 記述 |

| Model_type | はい | バッファのタイプの定義(入力、出力、入出力など) |

| Polarity | いいえ | このバッファによる信号駆動の極性 |

| Enable | いいえ | このバッファの出力イネーブル信号の極性(もし、適用できるならば) |

| Vinl,Vinh | いいえ | バッファの入力論理閾値 |

| C_comp | はい | バッファの入力、または、出力容量。 C_comp の最小値と最大値に注意する。 C_comp_pullup,C_comp_pulldown,C_comp_power_clamp,C_comp_gnd_clampはオプション |

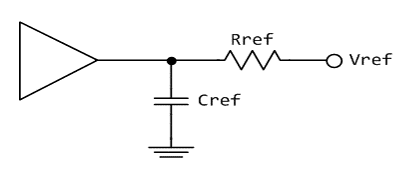

| Vmeas,Cref,Rref,Vref | いいえ | シミュレータに、このバッファのTco(対クロック出力遅延)計測時のテスト負荷を提供する |

Table 2.4 – Modelセクションのキーワード

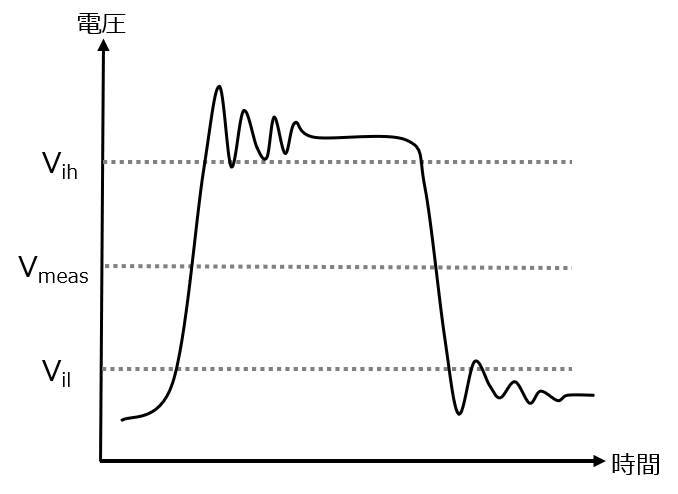

- Vinl, Vinh, Vmeas, C_comp, Cref , Rref , Vrefの定義は以下の通りです。

図-2.3 Vih , Vil , Vmeasの定義

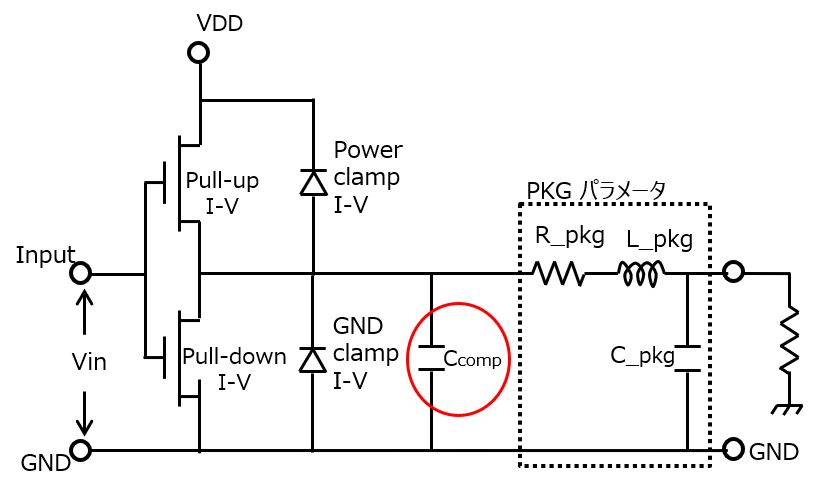

図-2.4 C_compの回路内位置づけ(赤丸)

図-2.5 Cref , Rref , Vrefの回路定義

C_compサブパラメータ

- C_compパラメータはバッファの容量を表し、最小、標準、最大の値を持つことができます。C_compは個別のバッファのトランジスタ、ダイパッド、ダイ上のインターコネクタの容量を表します。パッケージの容量は含みません。

- IBIS 4.0版では、4つのC_compサブパラメータとして、C_comp_pullup、C_comp_pulldown,、C_comp_power_clamp及びC_comp_gnd_clampが導入されました。これらのサブパラメータは、I/Oパッドと4つの供給リファレンス、[Pullup Reference]、[Pulldown Reference]、[Power Clamp Reference]、[GND Clamp Reference]のいずれかの部分に分かれていますが、電源の分配ネットワーク解析のために非常に重要です。

(引用:SIシミュレーションモデル解説書 P23~25)

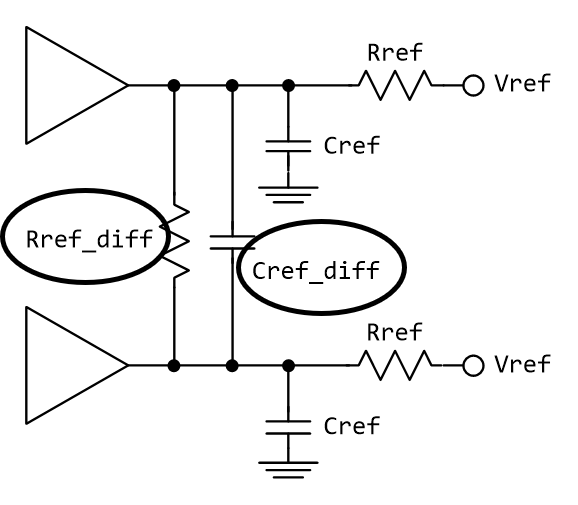

Rref_diff, Cref_diff サブパラメータ

- Rref_diff及びCref_diffサブパラメータは、差動バッファのタイミングテスト時のテスト負荷を表します。

- 同一の2つのモデルが、 [Diff Pin]キーワードで接続された場合のみ使用されます。

- Rref_diff及びCref_diffサブパラメータは、Rref, Cref, Vrefとともに組み合わせて使用できます。

図-2.6 Rref_diff, Cref_diffの回路定義

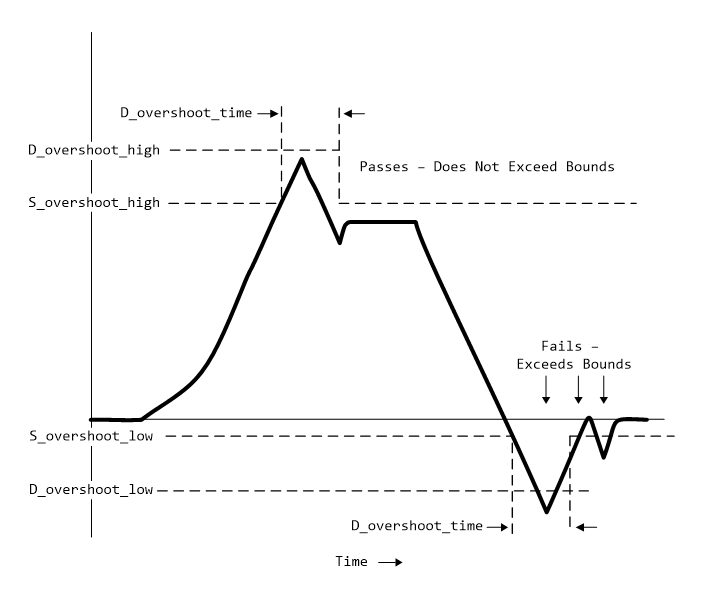

Model Spec

| キーワード: | [Model Spec] |

| 必須: | いいえ |

| Sub-Params: | Vinh, Vinl, Vinh+, Vinh-, Vinl+, Vinl-, S_overshoot_high, S_overshoot_low, D_overshoot_high, D_overshoot_low, D_overshoot_time, D_overshoot_area_h, D_overshoot_area_l, D_overshoot_ampl_h, D_overshoot_ampl_l, Pulse_high, Pulse_low, Pulse_time, Vmeas, Vref, Cref, Rref, Cref_rising, C_ref_falling, Rref_rising, Rref_falling, Vref_rising, Vref_falling, Vmeas_rising, Vmeas_falling, Rref_diff, Cref_diff, Weak_R, Weak_I, Weak_V |

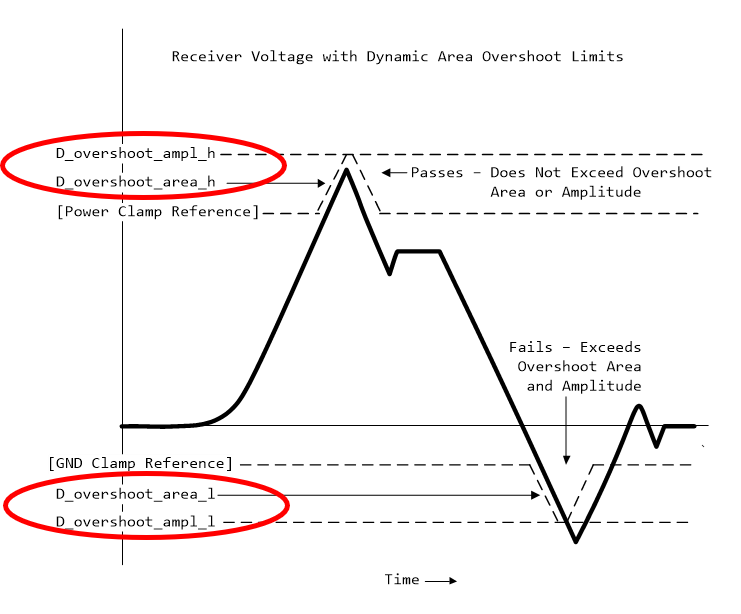

特にIBIS V5.1で追加された「area」や「ampl」について以下に図示します。

- D_overshoot_area_h : Dynamic overshoot high area (in V-s)

- D_overshoot_area_l: Dynamic overshoot low area (in V-s)

- D_overshoot_ampl_h: Dynamic overshoot high max amplitude

- D_overshoot_ampl_l : Dynamic overshoot low max amplitude

図-2.7 V3.2の仕様

図-2.8 V5.1で追加された「ampl」「area」

Receiver Thresholds

| キーワード: | [Receiver Thresholds] |

| 必須: | いいえ |

| Sub-Params: | Vth, Vth_min, Vth_max, Vinh_ac, Vinh_dc, Vinl_ac, Vinl_dc, Threshold_sensitivity, Reference_supply, Vcross_low, Vcross_high, Vdiff_ac, Vdiff_dc, Tslew_ac, Tdiffslew_ac |

尚、ここでは特に重要と判断される次のシンタックスについて補足します。

Vth, Vth_min, Vth_max, Vinh_ac, Vinh_dc, Vinl_ac, Vinl_dc

- [Receiver Thresholds]キーワードの意味は以下の通りです。

- Vth(*1) それぞれの閾値の電圧

- Vth_min(*1) それぞれの閾値の電圧の最小値

- Vth_max(*1) それぞれの閾値の電圧の最大値

- Vinh_ac(*2) レシーバの波形がLowからHighに移行する閾値

- Vinh_dc(*2) レシーバのHighのステートを保証する閾値

- Vinl_ac(*2) レシーバの波形がHighからLowに移行する閾値

- Vinl_dc(*2) レシーバのLowのステートを保証する閾値

(*1)Vref

(*2) Vthからのオフセット電圧値

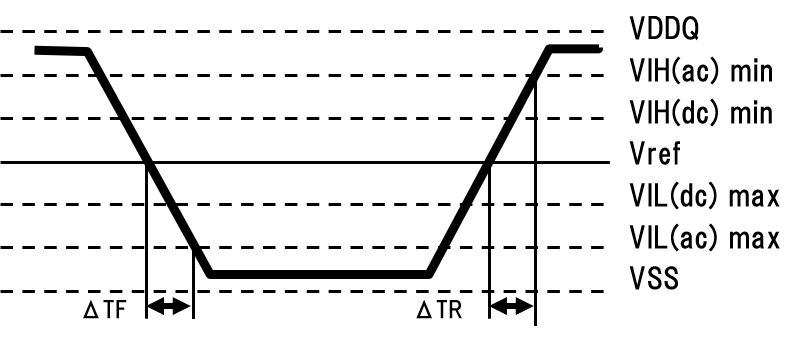

Falling Slew = (Vref – VIL(ac)max) / ΔTF

Rising Slew = (VIH(ac)min – Vref) / ΔTF

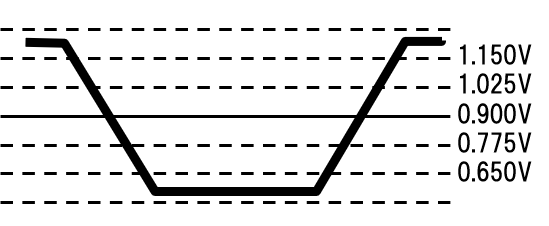

図-2.9 Receiver Thresholdsの定義

- 本キーワードで、DDRメモリインタフェースの判定値が定義出来ます。

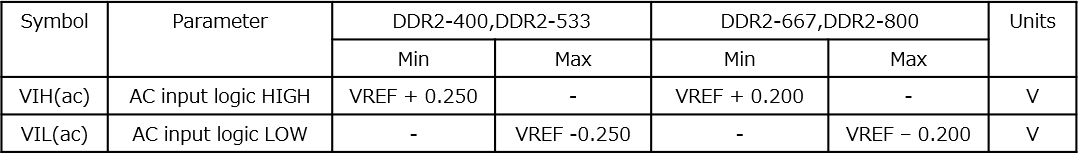

使用例 JEDEC(JESD79-2C)より抜粋(DDR2)

– AC閾値電圧

(JEDEC)Table 20 – Input AC logic level

上記の場合に、IBISに定義されるAC閾値電圧

- DDR2-400,DDR2-533

- Vinh_ac = 0.25V

- Vihl_ac = -0.25V

- DDR2-667,DDR2-800

- Vinh_ac = 0.2V

- Vihl_ac = -0.2V

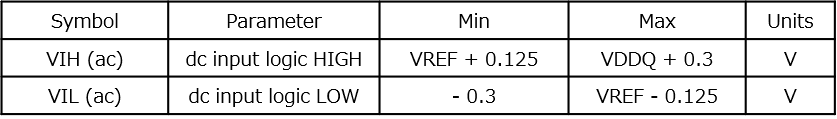

– DC閾値電圧

(JEDEC)Table 19 – Input DC logic level

上記の場合に、IBISに定義されるDC閾値電圧

-

- Vinh_dc = 0.125V

- Vihl_dc = -0.125V

- DDR2-400,DDR2-533の場合の[Receiver Thresholds]定義は以下の通りです。

[Receiver Thresholds]- Vth = 0.9V (Typの基準電圧)

- Vth_min = 0.882V (Minの基準電圧)

- Vth_max = 0.918V (Maxの基準電圧)

- Vinh_ac = 0.25V (Vthを基準としたHighレベルAC閾値)

- Vinh_dc = 0.125V (Vthを基準としたHighレベルDC閾値)

- Vinl_ac = -0.25V (Vthを基準としたLowレベルAC閾値)

- Vinl_dc = -0.125V (Vthを基準としたLowレベルDC閾値)

- 上記の例の場合、Typ 時のDC、ACの閾値の考え方は以下の通りです。

- AC :Vinh :0.900V + 0.250V = 1.150V

- AC :Vinl :0.900V - 0.250V = 0.650V

- DC :Vinh :0.900V + 0.125V = 1.025V

- DC :Vinl :0.900V - 0.125V = 0.775V

図-2.10 Typ時の例

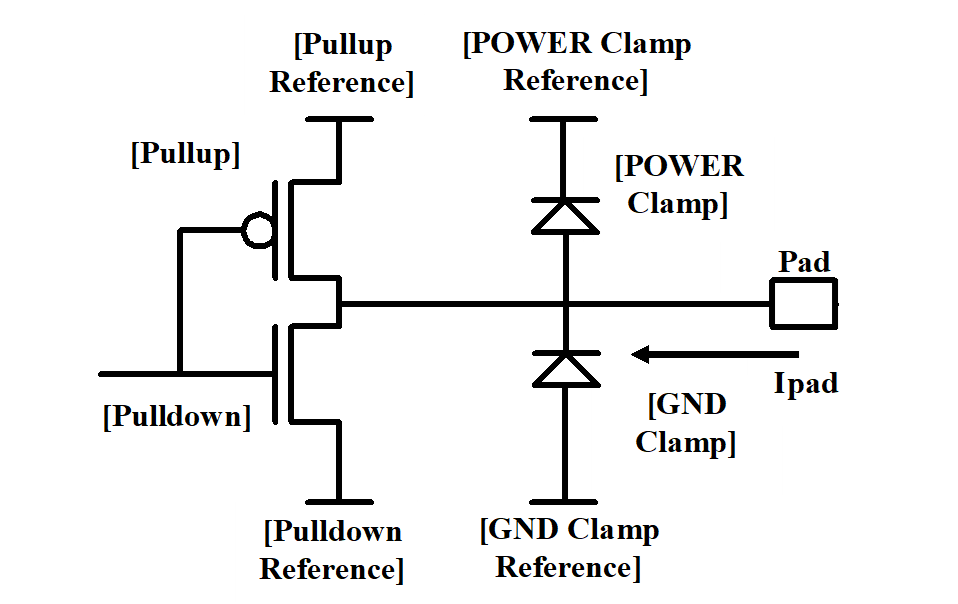

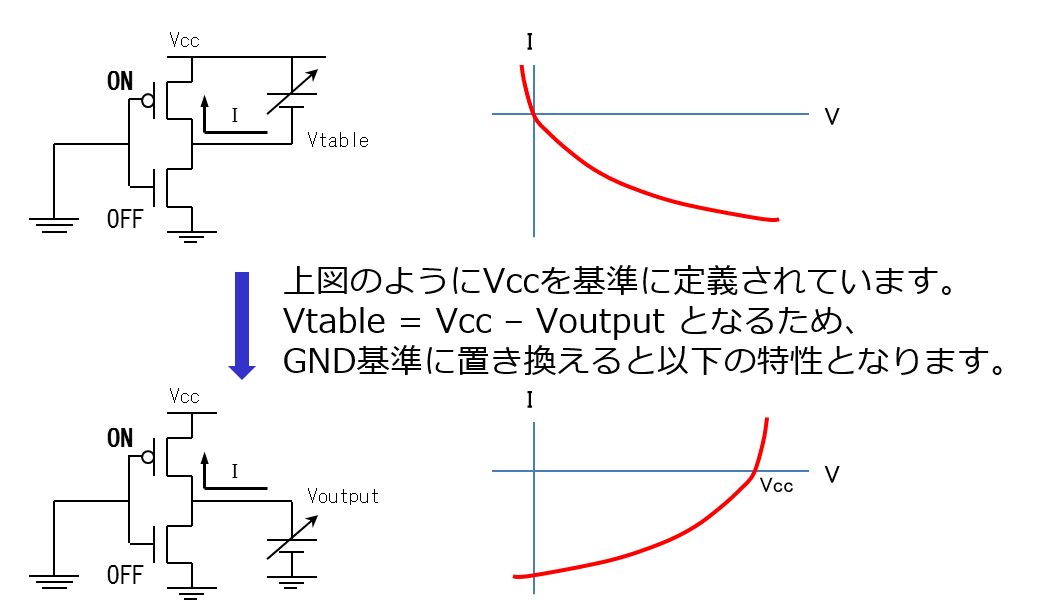

Pulldown, Pullup, GND Clamp, POWER Clamp

| キーワード: | [Pulldown], [Pullup], [GND Clamp], [POWER Clamp] |

| 必須: | はい(モデル内にこれらが存在する場合) |

| 概要: | 出力バッファのPulldown、Pullup構造のI-V特性テーブルと、GNDや電源ピンに接続されるクランプダイオードのI-V特性テーブルを定義します。電流は部品に流れ込む方向を正の値とします。 |

図-2.11 モデルキーワード構成の概念図

| キーワード | 必須 | 記述 |

| [Pulldown] | いいえ | 論理が“low”状態におけるバッファの出力I-V特性を表すためのデータ。このキーワードは、InputやOpen_Sourceバッファに対しては用いられず、モデルのタイプに依存してクランプの効果が含まれるか、含まれないか決まる。このキーワードに対するデータは、GNDを基準とし、もし、[Pulldown Reference]が存在するときはそれを基準とする。 |

| [Pullup] | いいえ | 論理が“high”状態におけるバッファの出力I-V特性を表すためのデータ。このキーワードは、InputやOpen_Sinkバッファに対しては用いられない。モデルのタイプに依存してクランプの効果が含まれるか、含まれないかが決まる。このキーワードに対するデータは、Vccを基準とし、もし、[Pullup Reference]が存在するときはそれを基準とする。 |

| [GND Clamp] | いいえ | バッファの入力、または、出力がハイインピーダンスの状態にあるときのI-V特性。電圧スイープは、GNDを基準とし、もし、[GND Clamp Reference]が存在するときはそれを基準とする。 |

| [POWER Clamp] | いいえ | バッファの入力、または、出力がハイインピーダンスの状態にあるときのI-V特性。電圧スイープは、Vccを基準とし、もし、[Power Clamp Reference]が存在するときはそれを基準とする。 |

(引用:SIシミュレーション・モデル解説書 P54)

Table 2.5 – [Model] I-Vテーブルのキーワード

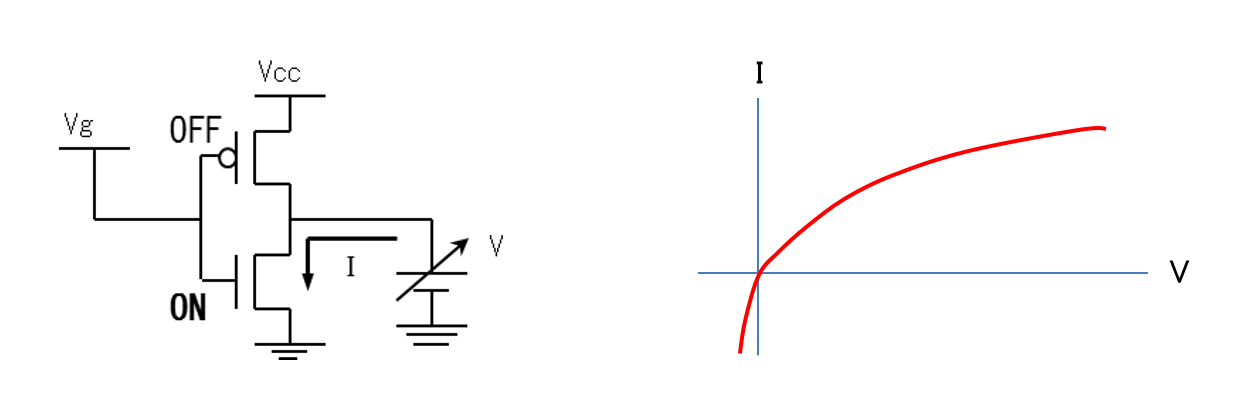

- Pulldownでは、下図のように、出力が “low” となるときのI-V特性を記述しています。

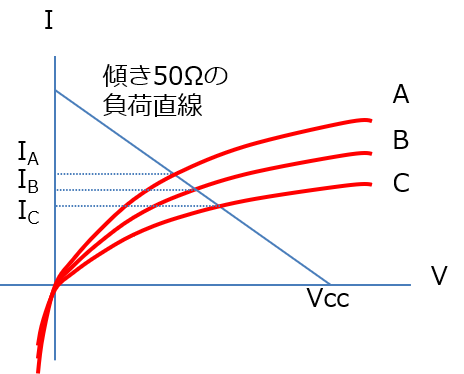

図-2.12 Pulldownの測定回路と特性図

- 右図は、駆動能力の異なる3種類のバッファ(A, B, C)のPulldown特性を重ね描きしたものです。50Ωの負荷(伝送線路)を接続したときに、high→low にスイッチングするときの電流は、電源電圧Vccを通る傾き50Ωの負荷直線と、Pulldown特性との交点の電流値、それぞれIA, IB, IC となります。

- この図の例では、同じ50Ω負荷を接続した場合に、最も多くの電流(IA)の流れるバッファAが、最も駆動能力が高いと言えます。

- Pullupでは、下図のように、出力が “high” となるときのI-V特性を記述しています。

図-2.13 Pulldown特性と駆動能力の関係

図-2.14 Pullupの測定回路と特性図

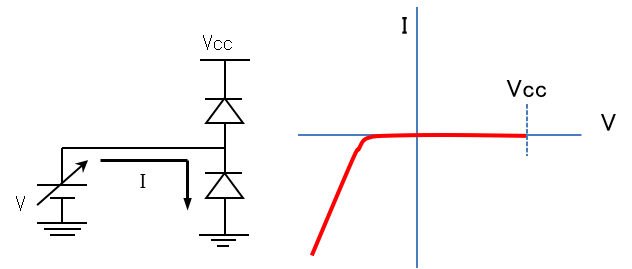

- GND Clampでは、下図のように、GNDに接続されたクランプダイオードのI-V特性を記述しています。

図-2.15 GND Clampの測定回路と特性図

- Power Clampでは、下図のように、電源に接続されたクランプダイオードのI-V特性を記述しています。

図-2.16 Power Clampの測定回路と特性図

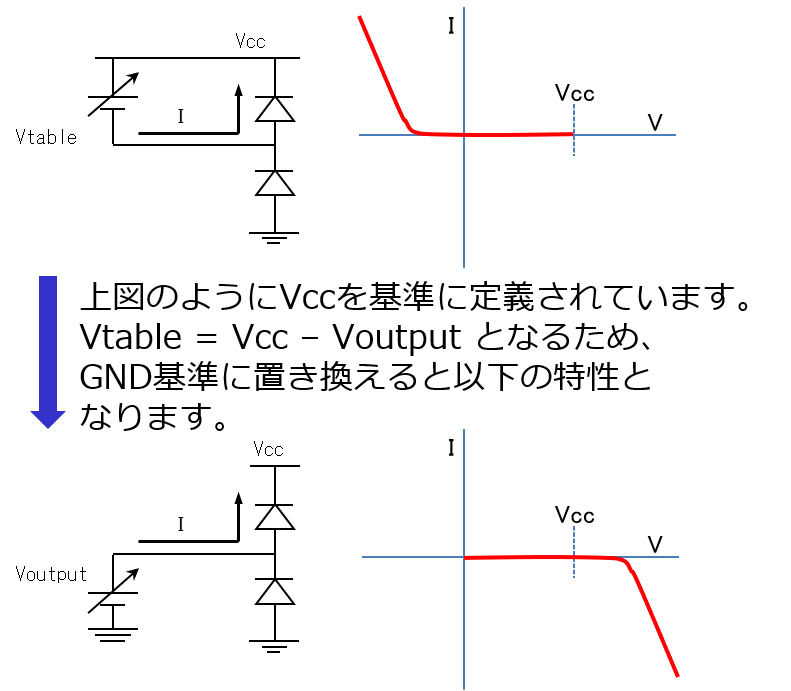

ISSO PD, ISSO PU, Composite Current

| キーワード: | [ISSO PD], [ISSO PU] |

| 必須: | いいえ |

| 概要: | [ISSO PD]では、pulldown reference(GND)の電圧を基準にした関数として、pulldown構造の実効電流を定義します。 [ISSO PU]では、pullup reference(Vcc)の電圧を基準にした関数として、pullup構造の実効電流を定義します。 |

- PDN(Power Delivery Network)から急に電流を引き込んだときに発生する オンダイ電圧降下の影響を考慮することができます。

- IBIS 4.2までは、バッファが理想的な電源に接続されているという想定のモデルでSSOノイズを考慮したシミュレーションができません。

- IBIS 5.0で、SSOノイズを考慮したシミュレーションができるように、キーワード[ISSO_PD][ISSO_PU][Composite Current]が追加されました。

| キーワード: | [Composite Current] |

| 必須: | いいえ |

| 概要: | バッファの電源リファレンス端子から流れる、立ち上がり、立ち下がりエッジの電流波形を定義します。 |

- IBIS 4.2 までと大きく異なる点として、IBIS5.0ではプリ・ドライバの影響を考慮します。

- より正確に電流の振る舞いを再現します。(Power Aware IBIS v5.0)

図-2.17 電流経路図

Ramp

| キーワード: | [Ramp] |

| 必須: | はい(inputs, terminators, Series, Series_switchのModel Type を除く) |

| Sub-Params: | dV/dt_r, dV/dt_f, R_load |

| 概要: | 出力バッファの立ち上がり、立ち下がり時間を定義します。 パッケージの影響は含みませんが、C_compパラメータの影響は含みます。 |

| Rampの記述例

[Ramp] |

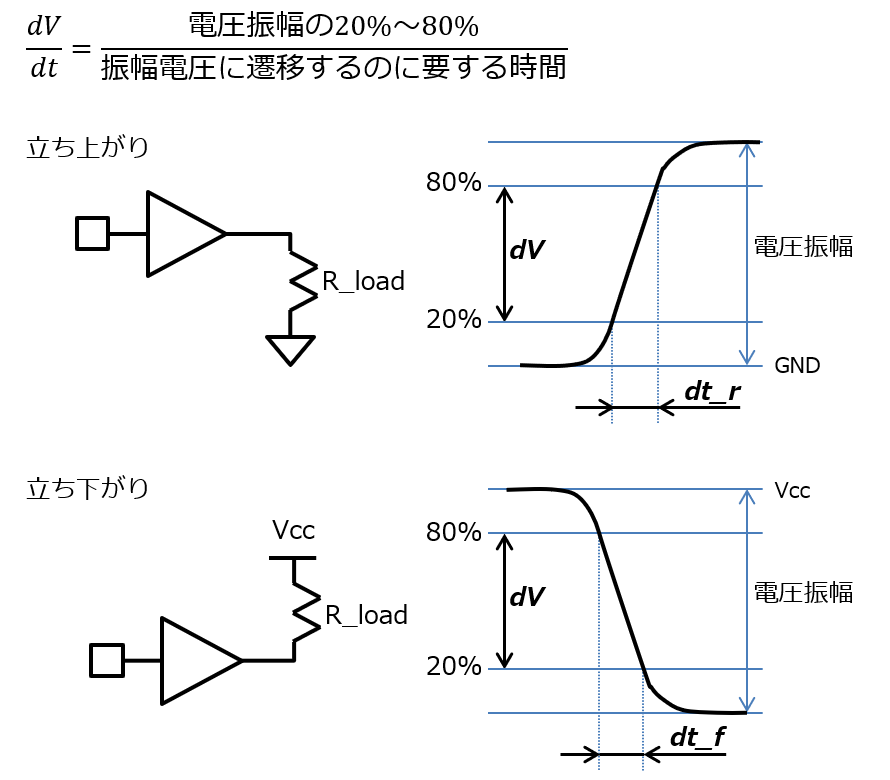

- RampのdV/dtの定義は以下の通りです。

図-2.18 Rampの測定回路と定義

Rising Waveform, Falling Waveform

| キーワード: | [Rising Waveform], [Falling Waveform] |

| 必須: | いいえ |

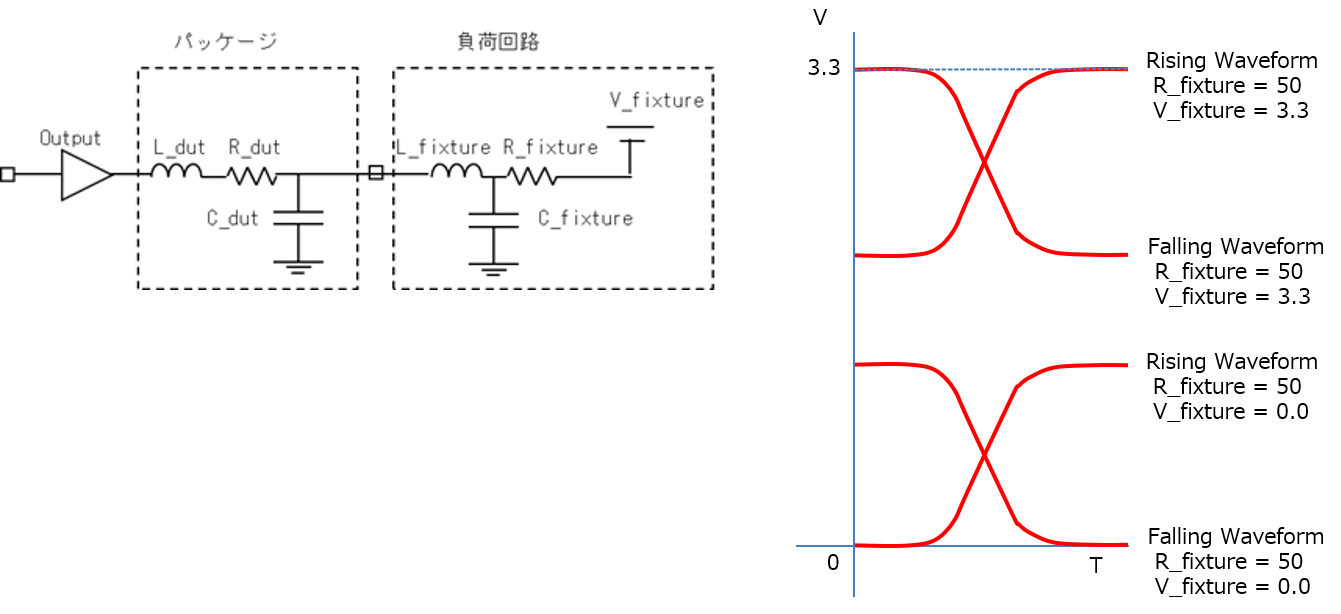

| Sub-Params: | R_fixture, V_fixture, V_fixture_min, V_fixture_max, C_fixture, L_fixture, R_dut, L_dut, C_dut |

| 概要: | 出力バッファの立ち上がり、立ち下がりのV-T波形を表します。 |

図-2.19 Waveformの測定回路と波形図

- 素子の立上り、立下り時間には、RampとWaveformの2通りの定義があります。

- 以下の理由から、一般的に[Rising Waveform] [Falling Waveform]のV-T特性は、[Ramp]よりも好ましいです。

- 単一の負荷抵抗と接続電圧のみからなる一組の[Ramp]データが、いずれの[Model]に対しても適用されるのに対して、V-T特性のデータは様々な負荷、接続電圧に対して提供されます。

- [Ramp]は、デバイスがON状態に変化するときのデータを供給するのみで、OFF状態に変化するときのデータは供給していません。V-T特性は両方の状態への変化を記述するのに用いられます。

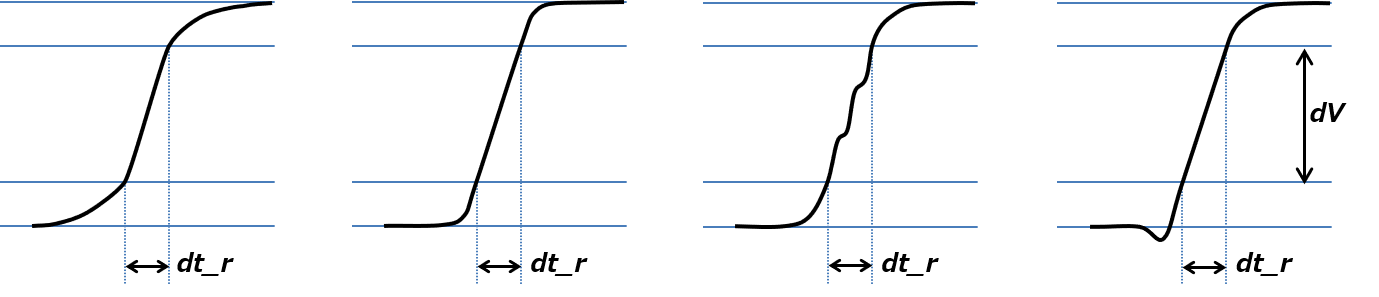

- [Ramp]は実際には、デバイスの有効平均を取るものであって、遷移の特性を詳細に表現するものではありません。

- 全体として遷移にかかる時間が同じであれば、理想的に線形の遷移特性も、棚状や階段状を示す他の遷移特性も同じ[Ramp]で表現されます。遷移の細部は、[Ramp]による表現では失われます(次項を参照)。

(引用:SIシミュレーション・モデル解説書 P62~63)

- 以下の特性は[Ramp]にすると全て同じ値となります。

図-2.20 Rampでは表現できない波形の違い

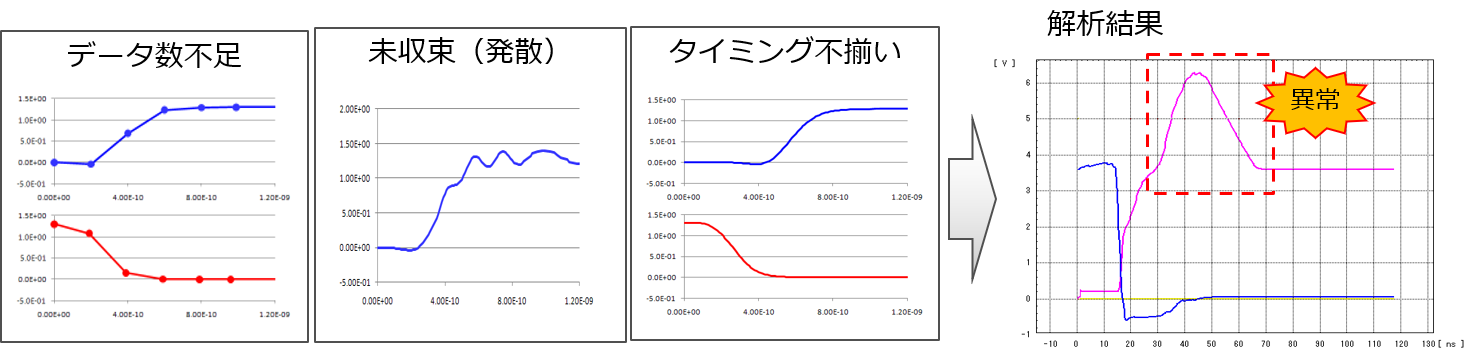

- Waveformの場合も、Waveformに正しくデータが定義されていることが条件となるため、以下のようなデータ異常がないことを確認のうえ使用してください。

図-2.21 Waveformデータ異常の例

まとめ

- IBISキーワードについて

- IBISファイルは大きく4つのセクションに分かれており、各セッションの中で多くのキーワードが定義されています。

- File Header Information :バージョンなどIBISの基本情報

- Component Description :汎用的なパッケージモデル、ピン-モデルリストなど

- Model Statement :V/I特性、過渡特性など

- Package Modeling :より詳細なパッケージモデル

- 必須と任意のキーワードがあり、規格で定義された全てのキーワードが、IBISファイルに使われている訳ではありません。

- IBISファイルは大きく4つのセクションに分かれており、各セッションの中で多くのキーワードが定義されています。